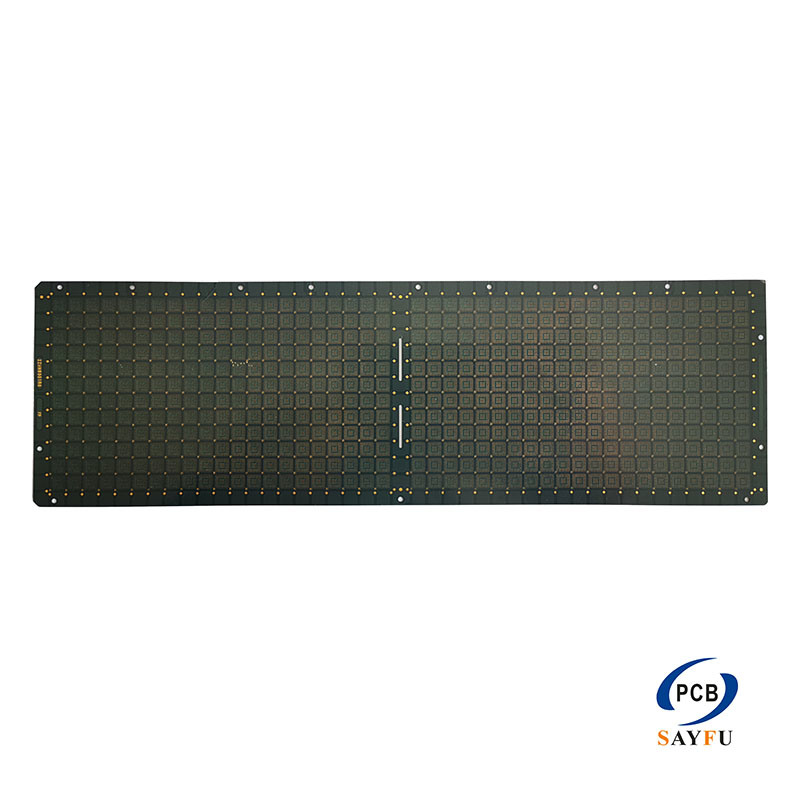

CSP(Chip Scale Package)

Images

General Specification:

Number of layers: 2/4 floors mainly

Structural features: thinner substrate core, more blind and buried via structures

Size: 44mm~1919mm

Board thickness: 0.1~0.4mm

Line width/line distance: 25/25 ~ 50/50 um

Gold finger spacing: 75~130 um

Surface treatment: Soft Au \ AFOP \ OSP

Special process: TLP, Etch back, VIP, VOP

DEFINE OF CSP IC Substrate

CSP IC Substrate is a type of single chip package with light weight and miniaturized scale, featuring similarly size with IC. CSP is mainly used in memory products, telecommunication products and electronic products with a small number of pins.

APPLICATION

Microprocessor/controller

ASIC (Application Specific Integrated Circuit)

Radio frequency devices

Storage (mobile electronic devices such as smart phones, digital cameras, etc.)

CSP is a chip-scale package, it is not a separate form of packaging, but a chip-scale package called when the chip area is comparable to the package area. The CSP package allows the ratio of chip area to package area to exceed 1:1.14, which is quite close to the ideal situation of 1:1, which is about 1/3 of the ordinary BGA; the center pin form of the CSP package chip is effectively shortened The signal conduction distance reduces its attenuation, and the anti-interference and anti-noise performance of the chip can also be greatly improved. In the CSP packaging method, the chip particles are soldered on the PCB board through solder balls. The PCB board has a large contact area, so the heat generated by the chip in operation can be easily conducted to the PCB board and dissipated.

Development prospects: Chip-scale packaging developed in response to the light, thin, short and small electronic products is a new generation of packaging methods. According to the development trend of electronic products, chip-scale packaging will continue to develop rapidly and gradually replace TSOP (ThinSmallOutlinePackage) packaging and Ordinary BGA package.